1. What is Amdahl’s Law? Assume that 30% instructions are data transfer instruction, 40 % instructions are ALU instruction and the rest are the control instruction. Each of data transfer, ALU and control instruction takes respectively 6clock cycle, 4clock cycle and 7 clock cycle. Find the CPI of the machine. If using latest hardware there found 3 times enhancement in the ALU instruction, then find the overall Speedup of the machine.

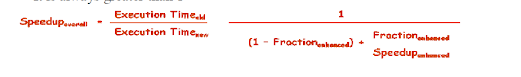

Amdahl’s Law:

Performance improvement gained from using some faster mode of execution is limited by the amount of time the enhancement is actually used

FRACTION ENHANCED :-Fraction of the computation time in the original machine that can use the enhancement

It is always less than or equal to 1

SPEEDUP ENHANCED:-Improvement gained by enhancement, that is how much faster the task would run if the enhanced mode is used for entire program.

It is always greater than 1

CPI = 0.3 * 6 + 0.4 * 4 + 0.3 * 7 = 5.5 (2.5 Mark)

Fraction Enhanced = 40% = 0.4

Speedup Enhanced = 3

Overall speed-up = 1 / [( 1 - 0.4 ) + ( 0.4 / 3 )] = 1.3636

2. Differentiate between array processor and multi processor with diagrams.

Ans:

Processor with diagram

Multiprocessor with diagram

3. Differentiate between two bit perdition and one bit prediction schemes with example.

Ans.

One bit prediction schemes with example

Use result from last time this instruction executed.

Let initial value = NT, actual outcome of branches is- T, T, T, T, T, NT

Predictions are:

NT, T,T,T,T,T

2 wrong (in red), 4 correct = 66% accuracy

Two bit perdition schemes with example

Change prediction only if twice mispredicted

Let initial value = NT, actual outcome of branches is- NT, T, NT, T

Predictions are:

NT, NT, NT, NT

2 wrong (in red), 2 correct = 50% accuracy

4. Find out the total no of clock cycles required to execute the following instructions without and with operand forwarding?

LD R1, 0(R2)

DADDIU R1,R1,#1

SD R1, 0(R2)

DADDIU R2,R2,#4

DSUB R4,R3,R2

ANS:

Without operand forwarding = 16 CYCLES

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 13 | 14 | 15 | 16 |

LD | IF | ID | E | M | W | | | | | | | | | | |

DADD | | IF | ID | S | S | E | M | W | | | | | | | |

SD | | | IF | | | ID | S | S | E | M | W | | | | |

DADD | | | | | | IF | | | ID | E | M | W | | | |

DSUB | | | | | | | | | IF | ID | S | S | E | M | W |

With operand forwarding =10 CYCLES

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

LD | IF | ID | E | M | W | | | | | | |

DADD | | IF | ID | S | E | M | W | | | | |

SD | | | IF | | ID | E | M | W | | | |

DADD | | | | | IF | ID | E | M | W | | |

DSUB | | | | | | IF | ID | E | M | W |

|

5. A five stage pipeline processor has IF, ID, EXE, MEM, WB. The IF, ID, MEM, WB stages takes 1 clock cycles each for any instruction. The EXE stage takes 1 clock cycle for LOAD, ADD & SUB instructions, 2 clock cycles for MUL and DIV instructions respectively.

Consider the following instructions:-

LOAD R3, 9(R2)

DIV R1, R3, R4

ADD R5, R1, R6

SUB R7, R1, R8

MUL R9, R1, R10

For the above sequence of instructions, find out total number of clock cycles required to complete the execution, without operand forwarding?

ANS:

6. In a five stage pipeline IF, ID, EX, MEM, WB; ADD, SUB and LOAD takes one clock cycle, MUL takes three clock cycles to execute. Then for

ADD R2, R1, R0

LOAD R7, 10(R3)

CO - 2

MUL R4, R7, R2

SUB R6, R5, R4

Calculate Number of clock cycles required using operand forwarding techniques.

ANS: